About one year ago while I was doing the PCB layout of some design, I found that I need to consider about the transmission line effect that the layout exhibit. I did some searching on the web, forum, and helped myself. I realize that this issue is very important especially when we do board design with high complexity involving high frequency circuit. So, in this post I want to summarize (write a note) of what I found. I may take a look here again if I need to handle another design in the future that posses the same issue.

Under certain condition, PCB trace/PCB interconnection ceased to act as a simple pair of wires and behaves as a transmission line. The length of interconnection and the highest frequency that the signal traversing the interconnection has are the determining factor that lead to the condition.

In communications and electronic engineering, a transmission line is a specialized cable or other structure designed to conduct alternating current or radio frequency, that is, currents with frequency high enough that their wave nature must be taken into account. (from Wikipedia)

What differentiates a pair of wires from a transmission line?

A short interconnection or one that operates at low frequency behaves as a group of lumped circuit elements, such as one capacitor and several resistors. The lumped circuit model is shown below:

A typical PCB interconnect resistance usually small and insignificant, so when we calculate the interconnection delay, we need to consider only the capacitance.

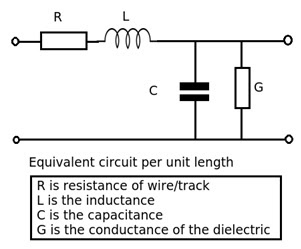

On the other case, if the interconnection is long or the signal frequency is high, the interconnection will behave as a transmission line, which has different characteristic. The transmission line model is shown below:

For example, at 1 Hz, a circuit that drives a 100 kΩ load through a long cable sees the cable merely as a 1Ω resistor in series with the 100 kΩ load. However, at 300 MHz, the driver sees only the cable’s characteristic impedance, which consists of a continuous uniform resistance, inductance, and a capacitance. The driver doesn’t see 100 kΩ load during the 300 MHz signal’s transitions.

The equivalent circuit for transmission line:

From the equivalent circuit above, the characteristic impedance can be derived, that is

( Note: the derivation of the formula involving Telegrapher’s Equation, wave equation and differential equation, since it quite complicated I cannot put it here, if we want to dig deeper we can read Wikipedia page about transmission line or googling another source )

As we can see from the equation, at high frequency the value of R and G is small compared to jwL and jwC and so it can be ignored, therefore resulting in an expression

, as we can see it is frequency independent and only depend on L and C.

How do we know when to treat the interconnection as a transmission line or a simple normal wire? How to judge it? And when will the transmission line effect occurred?

For analog signal, the rule of thumb is when the length of trace is 1/10 of the wavelength (it’s just approximation, there’re also some people that said it is 1/8). When the length of trace is less than 1/10 wavelength it is called short interconnection, when it is more than 1/10 it is called long interconnection. Long interconnection should be treated as a transmission line.

The wavelength can be calculated from the formula

, where c is the speed of light in free space ( 3 x 10^8 m/s ) and √2.3 factor came from dielectric material adjacent to the conductor.

For example, if we have a 32 inch ( 81 cm ) trace, then the wavelength is 320 inch ( 810 cm ), the interconnection can be treated as a lumped capacitor at signal frequencies as high as

A short length interconnection looks like a pair of wire and simple capacitor. The RC time-constant formula for the charging of a capacitor through a resistor determines the signal delay through a short or low-frequency interconnection. The resistance of a conductor on PCB is usually too small to consider, but you should include the driver’s output resistance in calculating the time constant. The interconnection propagation delay would be the time from the application of the new signal until the signal reaches the receiver’s switching threshold.

For digital signal, the rule of thumb is when the rise time of signal is less than round trip flight time ( twice the propagation delay ) then it should be treated as a transmission line. Round trip flight time is the time required for the signal’s electromagnetic wave to reach the end of interconnect then goes back to the source/driver.

Although the previous wavelength criterion illustrate the basic principle, this rise time rule is easier to use and should form the basis for deciding whether interconnection behaves as a transmission line. The reason is simple, all digital signals contain frequency components that is higher than fundamental. To have sharp corners, square waves contain at least third and fifth harmonics. Although you could use the frequency of these harmonics, digital-system designers think in rise and fall times, which are easier to measure with oscilloscope. If you can’t measure the rise and fall times, you can estimate them, typically 10 to 20% of the period.

Designers should not fall into the trap of thinking that their IC’s rise times are those on that data sheets. Most data sheets don’t even specify rise and fall times, but data sheets that do generally only provides the maximum (slowest) values. The parts that you receive are likely to be at least slightly faster and maybe several times faster. So, you should use rise time figure based on manufacturer’s guarantee or on your own tests.

For the earlier example, a 32 inch ( 81cm ) trace will have a propagation delay

, which is the time the electromagnetic wave make one-way trip. The 2tpd = 8,2 nanosecond, which is the time it make two-way trip ( round trip flight time ). So, if the rise time is less than 8,2 ns, then it is a transmission line. If you assume the rise time to be 20% of signal’s period ( 0,2T = 8,2 ns ), then the signal period is 41 ns, thus f = 1/T = 1/41 ns = 24 MHz. So, for signal higher than 24 MHz, this interconnection is a transmission line.

Transmission line issue : Signal Reflection

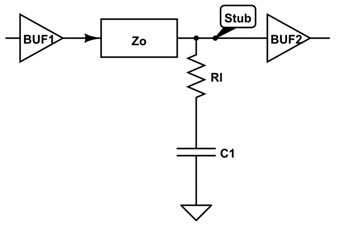

Below is the diagram of basic single ended transmission line:

As the wavefront travels along the transmission line it encounter the characteristic impedance ( Z0 ). When the wavefront reaches the end of the path, if a mismatch between ( Z0 ) and termination impedance ( Zt )exist, portions of the wave are reflected. As the wave reflects back along the transmission line, it eventually reaches the original source impedance ( ZS ). If a mismatch exist between the transmission line characteristic impedance ( Z0 ) and ZS, then portions of the wave are re-reflected. Simply said, if ZS , Z0 , and Zt are uncontrolled ( improperly terminated transmission line ) it can cause reflection, and potentially produce these type of distorted signal:

- Signals that exceed specified high level or low level threshold ( overshoot and undershoot ).

- Signals that has false edges ( ringing ).

- Signals that have reduced operating margins ( degradaded eye diagram caused by inter-symbol interference ).

- Also in extreme cases, physical damage or overheating at the driver / receiver components could happen.

How to properly terminate a transmission line to avoid reflection? What method should we use?

There’re several methods of line termination, the following schemes will describe it:

(1) Simple parallel termination

In this simple parallel termination scheme, the terminating resistor R1 is equal to transmission line characteristic impedance Z0.

Advantage : simple.

Disadvantage : added more load to the driver, it draw additional current from the driver.

(2) Series termination

In a series termination scheme, the resistor matches the impedance at the signal source instead of matching the impedance at each load. The sum of R1 and the impedance of the output driver should be equal to the Z0. Because silicon IC output impedances are low, you should add a series resistor to match the signal source to the line impedance.

Advantage : consumes less power.Disadvantage : rise time degrades due to the increased RC time constant.

(3) Thevenin parallel termination

This is the alternative to the parallel termination scheme which uses a Thevenin voltage divider. The terminating resistor is split between R1 and R2, which equal the line impedance when combined ( R1 || R2 ) = Z0.

Advantage: reduce the current drawn from the source driver compared to simple parallel termination scheme.

Disadvantage: increase the current drawn from the supply, because resistors are tied between VCC and GND.

(4) Active parallel termination

An active parallel termination scheme, the terminating resistor (R1 = Z0) is tied to a bias voltage (Vbias). In this scheme, the voltage is selected so that the output drivers can draw current from the high and low-level signals.

Disadvantage: this scheme requires a separate voltage source that can sink and source currents to match the output transfer rates.

(5) Series-RC parallel termination

A series-RC parallel termination scheme uses a resistor and capacitor (i.e., series-RC) network as the terminating impedance. The terminating resistor (R1) is equal to Z0. The capacitor must be large enough to filter the constant flow of DC current. However, if the capacitor is too large, it will delay the signal beyond the design threshold. Capacitors smaller than 100 pF diminish the effectiveness of termination. The capacitor blocks low-frequency signals while passing high-frequency signals. Therefore, the DC loading effect of R1 does not have an impact on the driver, as there is no DC path to ground.

Disadvantage: Not all drivers can handle the dynamic current requirements for larger capacitor loads.

How to calculate the value of characteristic impedance? Some peoples said it must be 50 Ohm, why?

When written in the IC datasheet that we need to design our PCB traces with a controlled-impedance, then we’re designing to compensate the transmission line. If the impedance of a trace is matched to the output impedance of IC or source, then we reduce the possibility of reflections which would lead to standing waves on the trace and cause all sorts of headaches. The controlled- impedance for single ended by convention is 50 Ω and for differential pair 100 Ω. It has become the standard when designing transmission line since back then. There’re various stories about how & why the value 50 Ω was chosen. It’s a compromise between low attenuation and power handling.

Within reason, the absolute impedance value chosen is not normally important, providing it is controlled along the entire length of the line. Other constraints in a design often dictate the impedance for us; it may be chosen based on a design specification (e.g. 65 Ω for PCI) or chosen to reduce current (a high impedance). It will generally be between 45 and 80 Ω due to typical material geometries, and if the signal changes layer then the trace geometry should be adjusted as necessary to maintain a consistent Z0.

To calculate characteristic impedance there’s online tool that I found “PCB Microstrip Impedance Calculator”:

Below is the example when I tried:

Specific case: Termination of CCLK signal for configuration of Spartan 6 FPGA

This was actually the design issue that I need to consider about one year ago. CCLK pin is used for clock signal during the configuration process of Spartan 6 FPGA. It usually connected to SCK pin of SPI Flash ROM. It has max frequency of 26 MHz. In the Xilinx documentation, it’s suggested to use Thevenin parallel termination with 100 Ω res connected to GND and 100 Ω res tied to 3.3V supply. The bad thing about this is it will bias the CCLK node to VCCO/2 = 3.3 V/2 = 1.65 V. This is not good because it will result in constant current at post-configuration. ( unnecessary power consumption )

There’s a guy at Xilinx forum that suggested a simple way to avoid the constant current drawn. The simple way is to AC coupled the 50 Ω termination Res to GND with a cap. A value of 0.1 uF or 0.01 uF should work fine, lower values should work as well. ( just make sure the time contant is longer than the rise/fall time of the CCLK signal )

Other version is to add two cap for the Thevenin termination like shown in this figure:

The capacitor will block the DC signal, so there will be no current drain at post-configuration.

This method is good for multiple-load clock lines. For single-driver, single load CCLK routing, a 33 Ω series resistor ( placed at near the driver pin ) is an even simpler termination option. When you consider ~15 Ω source impedance of the signal driver, the net series termination is close enough to 50 Ω. ( Note: the nominal for source impedance of the signal driver can be calculated from the Xilinx-supplied IBIS model )

References:

- wikipedia.org/wiki/Transmission_line

- electronicstackexchange forum

- Xilinx forum

- National Instruments white paper "Proper Termination for High Speed Digital I/O Application"

No comments:

Post a Comment